(VFO with DDS – Direct Digital Synthesizer)

En este artículo escribo sobre lo que es una verdadera maravilla tecnológica, gracias a la cual hoy podemos hacer sintetizadores de señal de gran versatilidad, precisión y estabilidad con hardware reducido. Es el llamado Sintetizador Digital Directo (o Direct Digital Synthesizer DDS).

Esta modalidad de síntesis de señales poco a poco ha ido reemplazando a los clásicos circuitos PLL (lazo enclavado en fase), debido a su mayor capacidad de resolución en frecuencia y fase (y también de amplitud en algunos modelos de DDS). Gracias a estas cualidades es posible construir en forma más sencilla transmisores de gran estabilidad, receptores de precisión para instrumentación y moduladores para señales complejas como QAM, entre otras cosas.

Analizaremos brevemente aspectos teóricos de su funcionamiento y finalmente veremos cómo construir uno para nuestro uso en experimentación. Al final de esta página podrás encontrar los links de descarga con toda la información necesaria para que hagas tu propio oscilador local DDS, basado en el módulo AD9850 @ 125 MHZ..

Ahora bien… ¿Cómo funciona un sintetizador digital directo? veamos un poco de teoría…

Oscilador Numéricamente Controlado (NCO)

El corazón del proceso de síntesis digital directa es el llamado Oscilador Numérico Controlado (NCO por sus siglas en inglés). A continuación describo brevemente como opera:

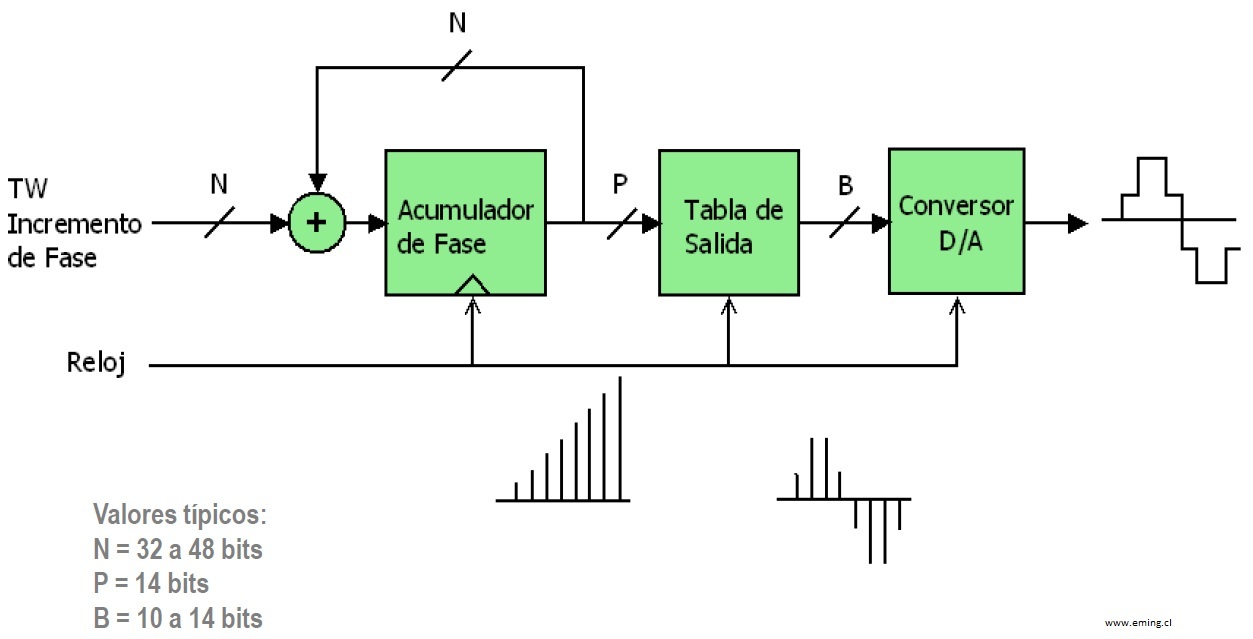

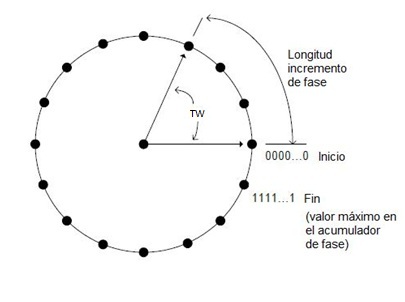

Vamos a la figura 1. Un registro (número) de N bits, llamado acumulador de fase, con cada ciclo de reloj se incrementa en un cierto valor que denominaremos incremento de fase TW. El acumulador de fase puede tener un valor – expresado en números decimales – entre 0 y 2^N – 1 (2 elevado a N, menos 1). Este incremento periódico del valor numérico contenido en el acumulador de fase hará que luego de determinada cantidad de ciclos de reloj alcance su valor máximo 2^N – 1. Mientras mayor sea el valor de TW, se requerirán menos ciclos de reloj para llegar al valor máximo del acumulador de fase, el cual una vez alcanzado hace que el valor del acumulador de fase vuelva a reiniciar a la siguiente suma de TW (siguiente ciclo de reloj). Podemos hacer la analogía entre el acumulador de fase y el ángulo de un fasor que gira a incrementos constantes TW (ver figura 2), donde 0° es el valor numérico 0 y cuyos 360° equivalen a un valor 2^N (ver figura 2).

Si en el bloque denominado tabla de salida (figura 1) a cada valor contenido en el acumulador de fase asociamos un determinado valor de amplitud, por ejemplo una sinusoide, tenemos un oscilador digital sinusoidal. En la práctica, a cada valor contenido en el acumulador de fase se le considera una dirección de memoria apuntada hacia los datos contenidos en la tabla de salida, y son estos datos los que contienen la amplitud de correspondería al seno (o coseno) del ángulo equivalente al número contenido en el acumulador de fase. Como los valores típicos de N van desde los 32 hasta 48 bits, si asociáramos a cada valor posible en el acumulador de fase una determinada amplitud, ¡ocuparíamos excesiva memoria!, por lo cual en la práctica se consideran sólo los P bits más significativos (usualmente 14 bits en DDS comerciales).

El valor de TW no necesariamente será un divisor exacto de 2^N, por lo cual al completar un ciclo (giro completo del fasor mostrado en la figura 2) podría no empezar en valor 0 el siguiente ciclo, sino en una fracción de TW. En esencia, cuando con la siguiente adición de TW al acumulador de fase sobrepasa la capacidad numérica de este, simplemente se ignora el bit de acarreo (overflow en inglés) y el ciclo se inicia nuevamente desde un valor numérico correspondiente a la fracción de TW que se puede expresar en N bits, contenida en el acumulador de fase.

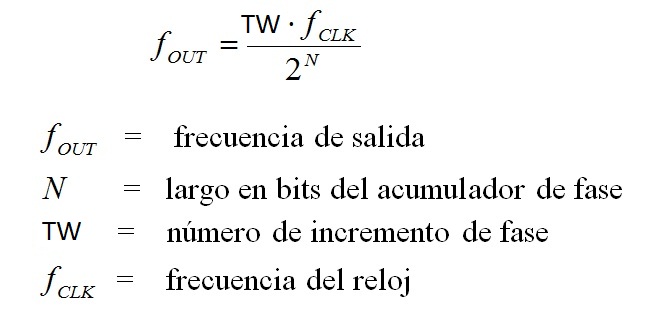

Según sea el valor contenido en el acumulador de fase, en cada ciclo de reloj se envía al conversor digital – analógico el valor correspondiente de la tabla de salida, obteniendo a la salida de este una sinusoide cuya frecuencia es función de TW (valor que controlamos externamente), la frecuencia de reloj (fija, definida por el hardware) y N (capacidad del acumulador de fase, también definido por el hardware). La ecuación que determina la frecuencia de salida es la siguiente:

Notar que para obtener frecuencias múltiplos exactos de 1 Hz, es necesario que la frecuencia de reloj sea una potencia de 2 – suponiendo exacta la frecuencia de reloj -. Sin embargo, para DDS con un acumulador de fase de 32 bits o más, la cantidad de frecuencias posibles es tan elevada que la resolución en frecuencia es muy fina (paso entre frecuencias posibles a generar por el DDS es de orden de fracción de Hz), con lo cual aunque utilicemos relojes de frecuencias comunes (125 MHz, por ejemplo) podemos aproximarnos a la frecuencia que se desea generar con error inferior a 1 Hz, más que suficiente para cualquier aplicación práctica.

Consideraciones respecto del espectro de salida de un DDS

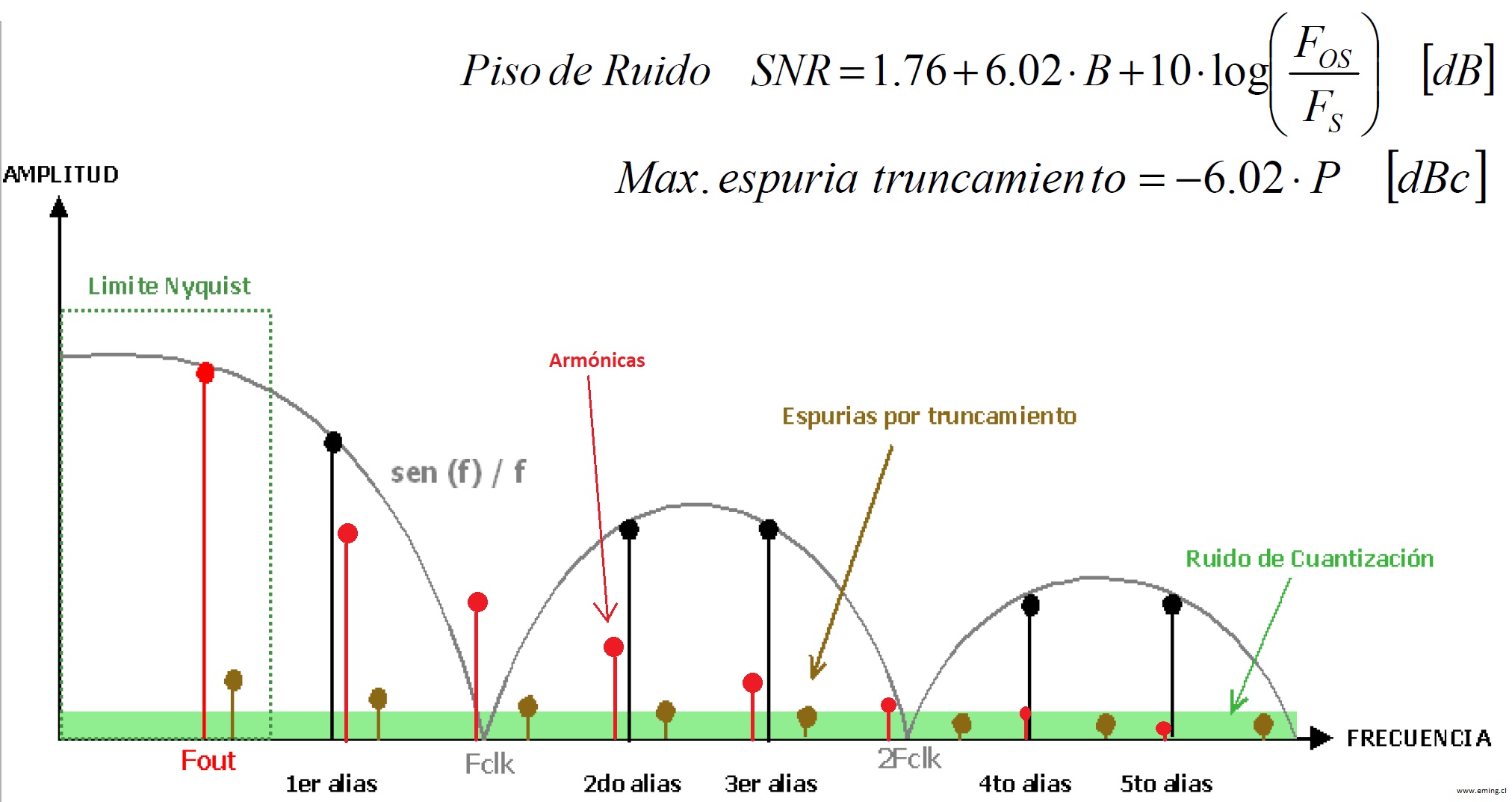

En la figura 3 tenemos un dibujo simplificado donde aparecen las principales componentes espurias que se generan en un DDS.

A continuación una breve descripción de cada una de ellas:

Frecuencias alias por digitalización de la señal. Por efecto alias, se observan componentes cuyas frecuencias están dadas por las sumas y restas de múltiplos de la frecuencia de muestreo (reloj fclk) y la fundamental (frecuencia de salida fout). El principal objetivo del filtro implementado en el módulo AD9850 es filtrar estas frecuencias imágenes.

Ruido de cuantización. El proceso de conversión digital a analógica, donde se obtiene un voltaje sinusoide, al tratarse de una señal digital tenemos que existe una diferencia entre el valor entregado por el conversor y aquel que debería tener la sinusoide. Este error de cuantización está determinado por la resolución del conversor D/A (típicamente entre 10 y 14 bits para DDS comerciales). Es razonable pensar que la potencia de ruido generada por este error de cuantización se distribuye uniformemente en toda la banda definida por el límite de Nyquist (es decir, desde 0 Hz hasta la mitad de la frecuencia de reloj Fclk/2), por lo cual es posible reducir el piso de ruido si se incrementa la frecuencia de reloj. En la figura 3 se representa el piso de ruido y la relación señal a ruido determinada por el error de cuantización, suponiendo un conversor D/A de B bits y Fs = 2*fout, donde Fos es la frecuencia de sobremuestreo (Fos > Fs), es decir, frecuencia a la cual se puede incrementar el reloj del DDS. En la práctica, por ejemplo, si Fs = fclk = 80MHz, teóricamente el valor máximo de la frecuencia de salida es fout = 40MHz (definido por límite de Nyquist), pero podemos mejorar la SNR teórica que define la resolución del conversor D/A a través del uso de una frecuencia de reloj más elevada, por ejemplo, fclk = 125MHz, pues distribuiremos la potencia de ruido de cuantización en un rango mayor de frecuencias (desde 0Hz hasta 62.5MHz). Otra forma de verlo es que, para una frecuencia de reloj fclk dada, la SNR definida por el ruido de cuantización será mayor cuando la frecuencia sintetizada fout sea mucho menor que el límite de Nyquist (fclk/2). Por ello, nos convendrá utilizar DDS con frecuencia de reloj elevada, aunque las frecuencias que queramos sintetizar sean mucho menores que la mitad de la frecuencia de reloj.

Espurias por truncamiento del número de fase. Como indiqué en un párrafo anterior, por motivos prácticos la tabla de salida del NCO no puede contener tantos registros como valores posibles tenga el acumulador de fase (piensen que para un acumulador de N = 32 bits necesitamos varios GB, y para N = 48 bits son centenares de TB!), y por esto existe un error en la conversión entre el ángulo de salida de la sinusoide (que considera sólo los P bits más significativos) y el ángulo contenido en el acumulador de fase. Este error tiene periodicidades, las que definen frecuencias espurias. En términos prácticos, aquella componente espuria de mayor amplitud estará a -6.02P dB de la frecuencia fundamental (fout), con típicamente P = 14 bits, y el número de incremento de fase equivalente de la mayor espuria por esta causa estará dado por el máximo común divisor entre el número de incremento de fase TW y 2^(N-P-1). Si el número de incremento de fase satisface que el máximo común divisor entre TW y 2^(A-P) es 2^(A-P), entonces no hay espurias por truncamiento de fase, ya que el error de ángulo sería constante en todo el ciclo (no hay periodicidad, por lo tanto no hay frecuencias asociadas).

No linealidades del conversor digital – análogo. Es imposible construir un conversor ideal, por lo que siempre – al igual que en los amplificadores – existirán componentes armónicas de la fundamental causadas por no linealidades en el proceso de conversión. En ciertas oportunidades pueden ser beneficiosas, pues las frecuencias armónicas son múltiplos de la frecuencia de salida, las que pueden ser utilizadas por la electrónica. Un buen ejemplo de aquello es la Application Note AN-543, donde se utilizan las componentes armónicas provenientes de un AD9850 (con frecuencia de reloj de 125 MHz, por lo tanto, con una frecuencia de salida teórica máxima de 62.5 MHz -límite de Nyquist-) para implementar un transmisor para radiodifusión sonora modulado digitalmente (que opera entre 88 y 108 MHz).

Jitter. A variaciones instantáneas de la frecuencia se le denomina «jitter», y en un DDS puede ser causado por el jitter propio del generador de reloj (por ello es importante utilizar aquellos que sean muy estables), por circuitos PLL de reloj (típicamente los DDS con frecuencias de reloj muy elevadas suelen utilizar circuitos PLL para multiplicar la frecuencia de reloj de entrada, generando jitter y ruido de fase). También se puede ocasionar por acoplamiento entre las pistas del circuito de reloj y fuentes externas de RF, o bien por ruido térmico.

En fin… como todo circuito electrónico, especialmente si conjuga señales analógicas y digitales, tenemos diversas causas que pueden generar componentes espurias. Lo ideal es asegurarse de construir un hardware debidamente protegido de las EMI, y tener una señal de salida que aproveche toda la escala del conversor D/A con una frecuencia muy inferior al límite de Nyquist (fclk/2).

Ahora vamos a encender el cautín… construyamos nuestro propio oscilador local con un sintetizador digital directo, basado en AD9850 de Analog Devices.

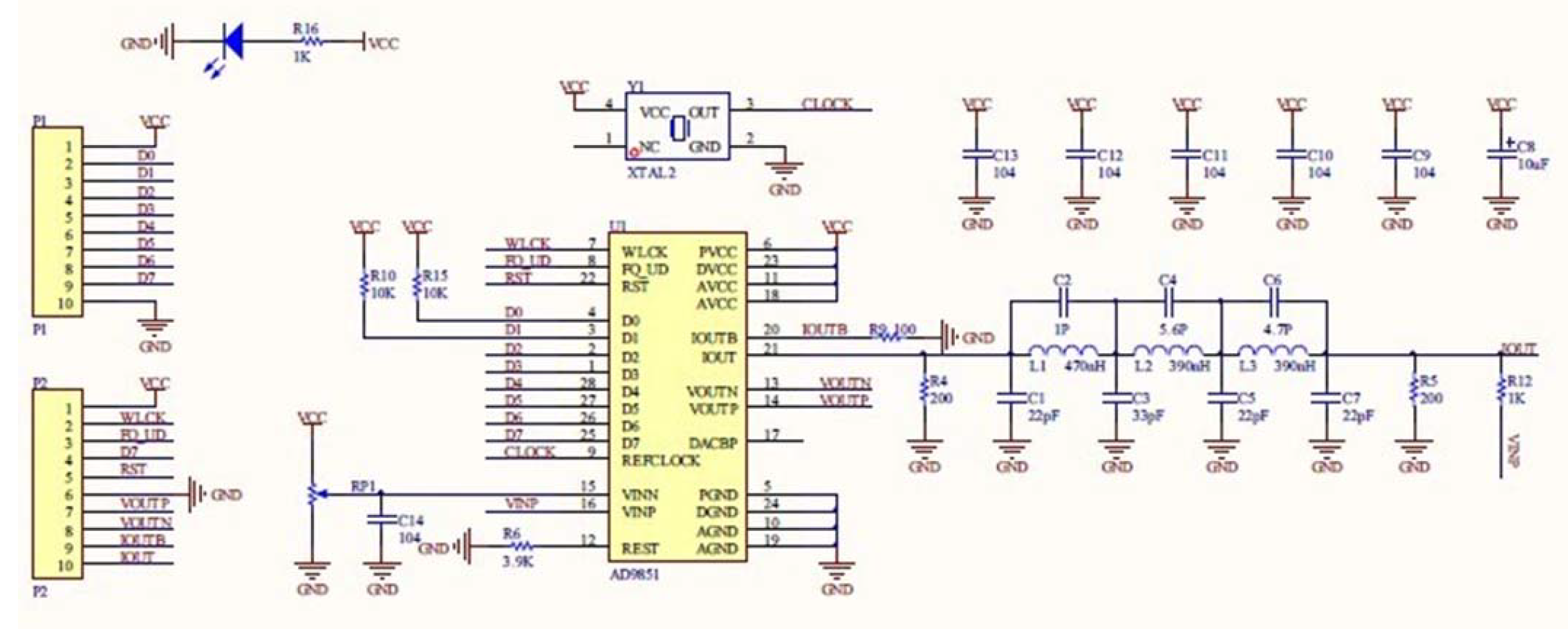

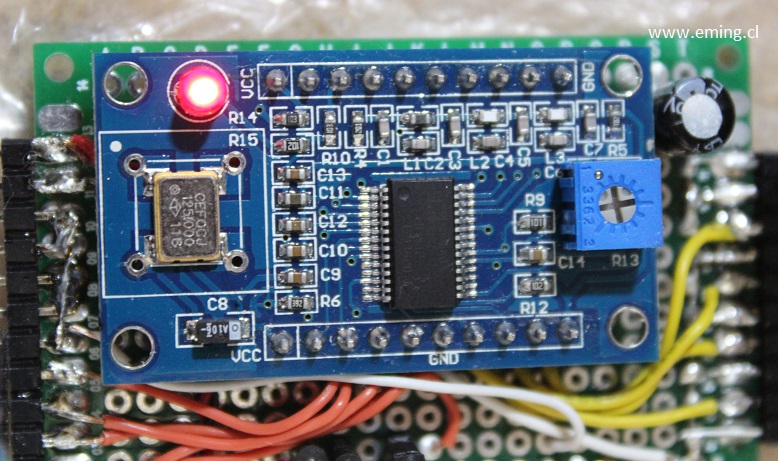

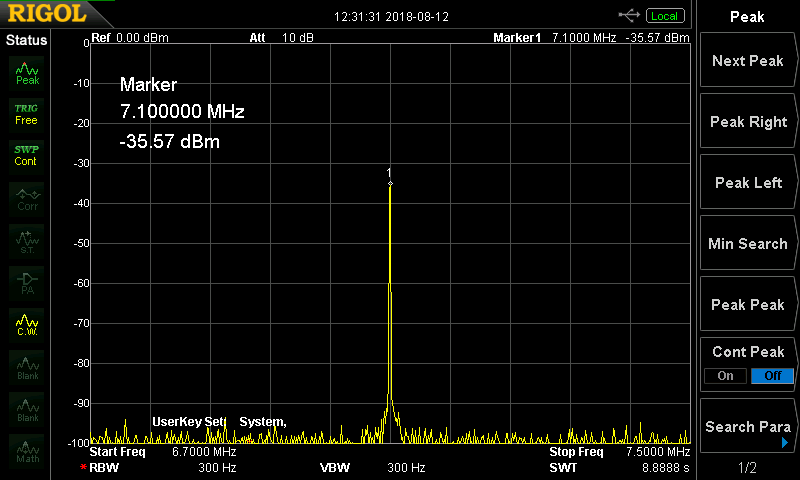

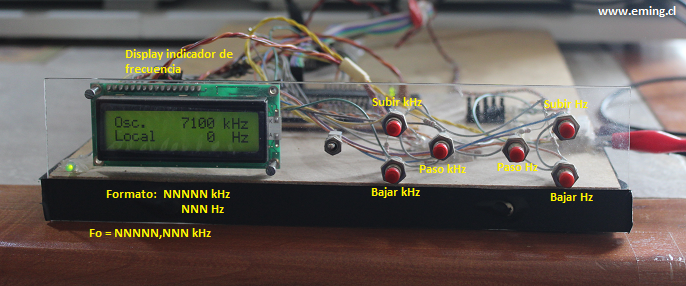

Este proyecto está basado en el módulo DDS AD9850 con reloj de 125 MHz, disponible por Ebay y Amazon. Puedes trabajar con instrumentos básicos (multímetro), una radio MF/HF y/o un SDR (como el famoso RTL) para «escuchar» las frecuencias que sintetizas. Aquí muestro mediciones con instrumentos debidamente calibrados (excepto el frecuencímetro del osciloscopio… no le crean… lee bien hasta 3 MHz… el analizador de espectro es mucho más confiable) con el objetivo que puedas visualizar los resultados que obtendrás.

Bueno… vamos al circuito:

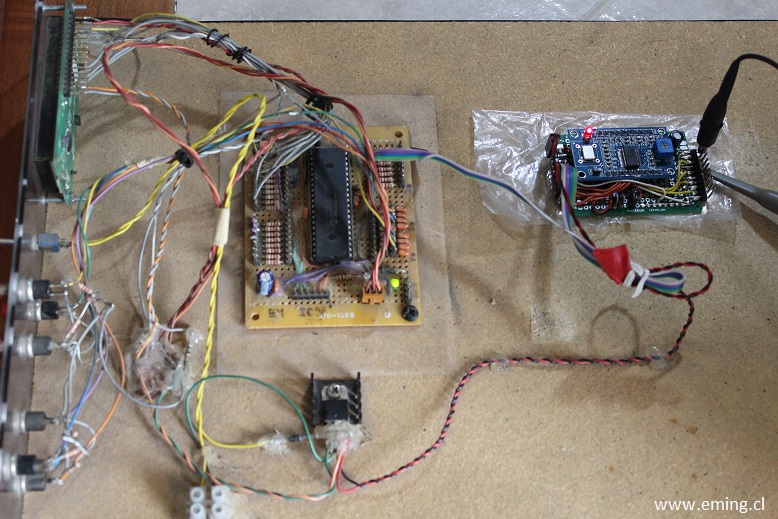

La tarjeta basada en PIC tiene muchos años… está reciclada de un proyecto que desarrollé en tiempos remotos. Si bien los microcontroladores PIC de la serie 16 son bastante «vintage» a estas alturas del partido, de vez en cuando los utilizo porque son muy confiables. Unos colegas me contaron que incluso algunos CubeSat que andan orbitando por la ionósfera tienen microcontroladores PIC en su interior 🙂 – aunque series más modernas -.

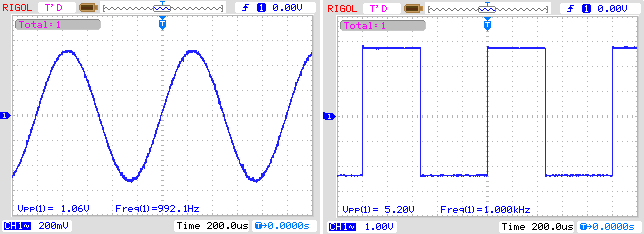

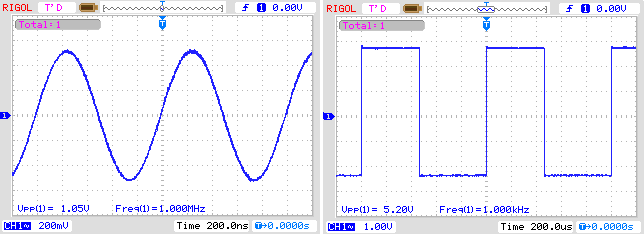

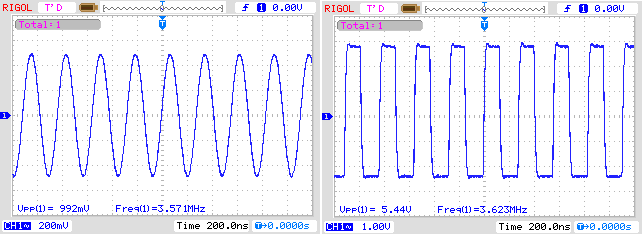

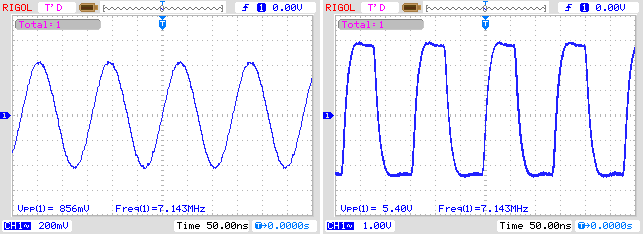

Y luego de mucho ensayo – error en la programación del PIC, tenemos los resultados que se muestran a continuación:

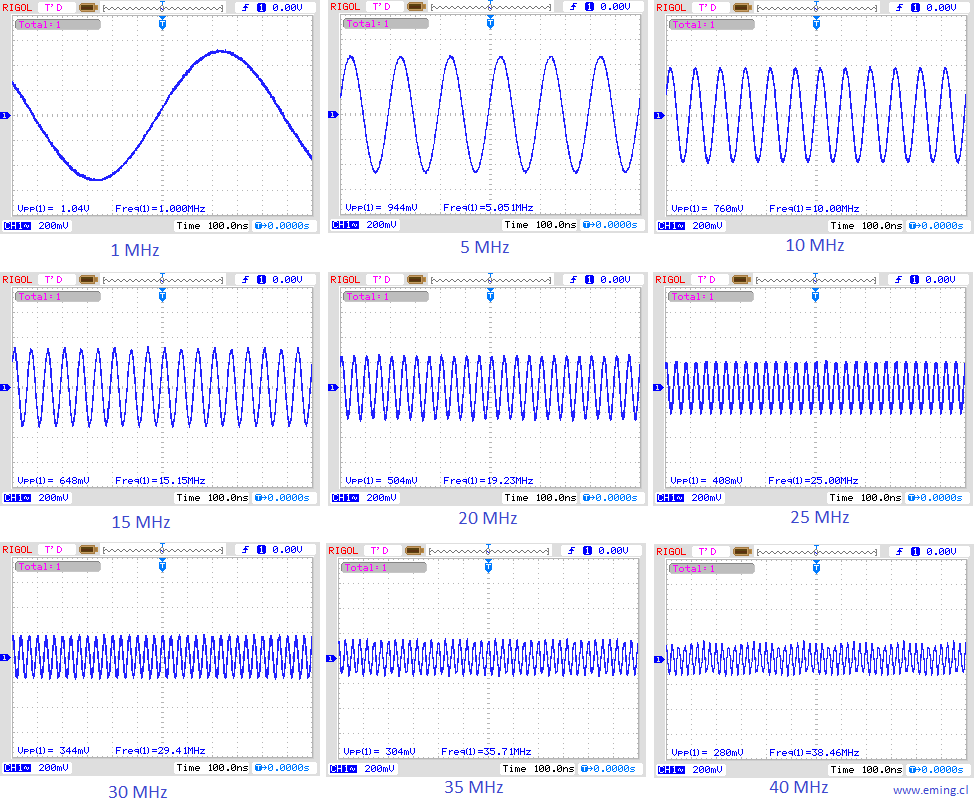

Formas de onda:

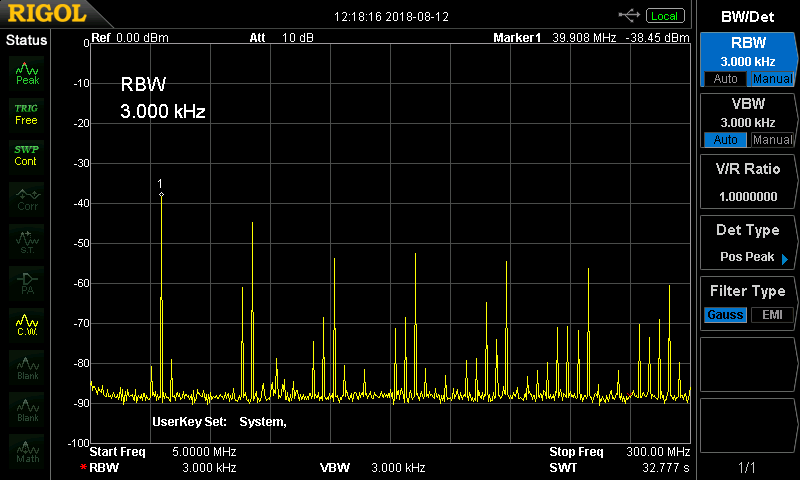

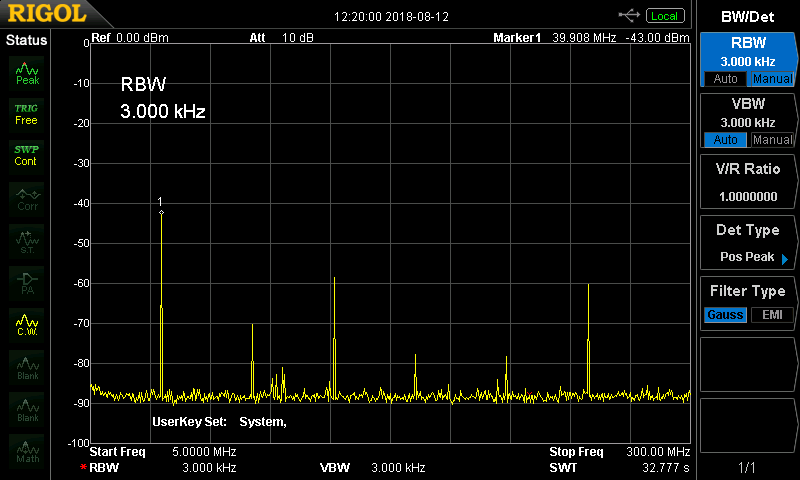

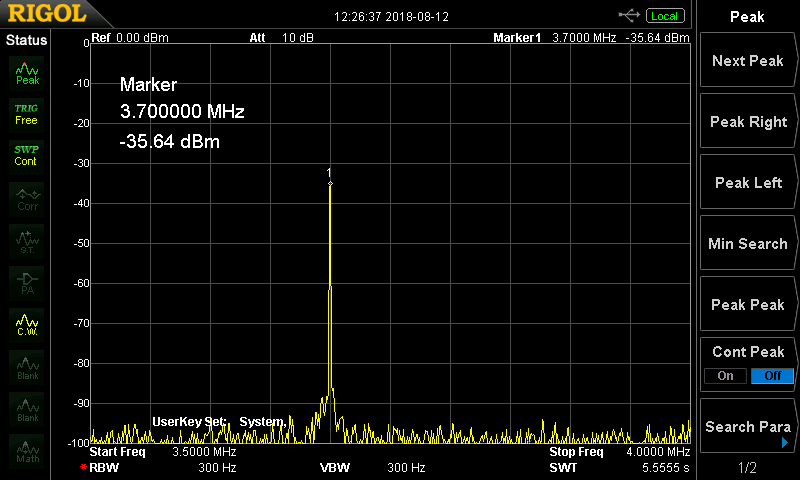

Espectro de salida:

Mi intención es probar este sintetizador como oscilador local para un transceptor SSB en kit que tengo ensamblado, pero actualmente en formato OFV con polivaricon. Es el Iler 40. Una maravilla que necesita de un buen OFV.

Comportamiento energético y térmico…

Luego de pruebas en diferentes frecuencias, noté que cuando generaba un fout mayor a 20MHz, el DDS se calentaba a temperatura sensible al tacto. Por ello, luego de dejar apagado el dispositivo unos minutos hasta que alcanzara temperatura ambiente, lo encendí con fout = 40MHz y, al minuto de operación y temperatura ambiente de 18°C, el AD9850 alcanzó una temperatura de 41.28°C. Por ello, estimo recomendable utilizar disipador térmico. Me parece buena opción ocupar estos que hay que el comercio para los chips del Raspberry Pi (esos que tienen un autoadhesivo para pegarse al chip).

Como observamos en la figura 11, a medida que incrementamos la frecuencia de salida, tenemos que la amplitud de la señal va disminuyendo. Algo diferente ocurre con el consumo de corriente. El circuito completo, es decir, DDS + reloj+ microcontrolador + display, operando a 1kHz consume 170mA aprox., a 1MHz se eleva a 190mA, y a 40MHz llegamos a los 210mA. Como no tenemos un incremento en la potencia de salida del DDS (de hecho, es al revés), no nos queda otra opción que la potencia adicional que consume el DDS se debe estar disipando en forma de calor. Por ello, me parece muy necesario poner aunque sea un pequeño disipador, sobre todo si la temperatura ambiente de donde se utiliza este oscilador es alta… y vamos que con el calentamiento global quizás a qué extremo vamos a llegar.

Algunas aplicaciones de esta tecnología pueden ser:

- Generadores de señal con modulaciones complejas, especialmente en DDS que permiten incorporar información en la amplitud. Un buen ejercicio sería implementar hardware donde se conecte un DDS con sus pines de programación paralela a una FPGA, de modo que podamos implementar circuitos de refresco de frecuencia, fase y amplitud de alta velocidad. Un circuito como este servirá para muchas cosas. ¡interesante futuro proyecto!.

- Oscilador local en transmisores y/o receptores de radio. Ideal para equipos de banda lateral única (SSB).

- Sintetizadores de audiofrecuencia de alta precisión.

- Instrumentos de medición, como analizadores de espectro y analizadores de antenas.

- Receptores de alta precisión para radioastronomía. Gracias a la gran cantidad de canales posibles, son una buena alternativa para construir receptores heterodinos que permitan hacer análisis de corrimientos de frecuencia por efecto Doppler para velocidades relativamente bajas. Con buenos filtros de frecuencia intermedia, podemos observar desplazamientos muy pequeños, del orden de los Hz.

¿Quieres construir tu oscilador local con DDS AD9850?:

Así quedó mi primer prototipo. En los links de descarga puedes encontrar la información necesaria para replicarlo.

Para minimizar espurias en la señal de salida, recomiendo montar la electrónica en una caja metálica a tierra y protegerla de RF producida en etapas de potencia y/o aquellas con conmutaciones digitales de alta velocidad. No olvides poner disipador térmico al DDS!!.

Links de descargas:

- Si te es mas cómodo tener en tu taller los circuitos impresos en papel, aquí los puedes descargar. Esquemáticos Oscilador Local en PDF.

- Archivo para cargar en PIC16F877A. Software para PIC (.hex).

Saludos y excelente semana,

Emerson Sebastián

felicidades por el logro,

una consulta como lograste la sincronización y transmisión de los datos con el pic desarrollaste una libreria o usaste el spi o i2c? desde ya gracias

Hola Emanuel!! Gracias por tu comentario.

Respecto a tu consulta… no usé spi o i2c, sino que generé un código en C para cargar el TW de acuerdo a las instrucciones que aparecen en el datasheet del AD9850 (ver páginas 12 y 13 en https://www.analog.com/media/en/technical-documentation/data-sheets/AD9850.pdf). No recuerdo donde guardé el código, pero era bastante sencillo. En la web dejé el .hex por si quieres implementar tu propio generador de señales.

Saludos y si necesitas ayuda, escríbeme.

Buena semana,

Emerson

Muy buen proyecto. Felicitaciones y gracias por compartir.

Gracias Julio César. Ya me daré el tiempo publicar otros circuitos en los que he trabajado. Saludos!!

Muchas gracias Edgardo. La idea es promover la experimentación en radio.

Felicitaciones por tu blog… muy interesante.

Saludos desde Talca!!

CD3EMT

Muy buena tu iniciativa. Gracias por compartirlo. LU1AR